## <u>Developer Manual</u> TMPA900 CPU Board

#### 2010 GLYN GmbH & Co. KG

All rights reserved. No part of this documentation may be reproduced or, with the use of electronic systems, edited copied or transmitted, in any form (print, photocopy, microfilm or another procedure) without the express authority of the GLYN GmbH & Co. KG, D-65510 Idstein.

The GLYN GmbH & Co. KG, D-65510 Idstein does not accept liability or provide any guarantee with respect to the contents of this documentation. The GLYN GmbH & Co. KG, D-65510 Idstein retains the right of revising this work. All programs and descriptions have been created to the best of our knowledge and tested with great care. However, errors cannot be entirely excluded. For this reason, the GLYN GmbH & Co. KG does not accept liability for possible errors and consequential damage resulting from the provision, performance or use of this material.

# **Table of Contents**

| 1.0 Revision List                                      | 4  |

|--------------------------------------------------------|----|

| 1.1 Contacts                                           | 4  |

| 2.0.0                                                  | _  |

| 2.0 Summary                                            | 5  |

| 2.1 Product Information TMPA900-CPU BOARD              |    |

| 2.2 Energy Consumption at 3.3V (preliminary values)    |    |

| 2.3 Block Diagram                                      | 6  |

| 2.4 TMPA900 CPU Board Reference Circuitry              |    |

| 2.5 Glyn's Graphic Base Board                          |    |

| 2.5.1 Glyn's Graphic Base Board Connectors             |    |

| 2.6 Instructions for use                               | 11 |

| 3.0 Operational Description                            | 12 |

| 3.1 CPU Core                                           |    |

| 3.2 Memory – Architecture                              |    |

| 3.2.1 Nand Flash Memory – Unique Characteristics       |    |

| 3.3 TMPA900CMXBG Block Diagram with Multilayer AHB     |    |

| 3.4 Power Supply                                       |    |

| 3.5 RESET                                              |    |

| 3.6 External power source control output               |    |

| 3.7 Ethernet - Network Controller                      |    |

| 3.8 UARTs                                              |    |

| 3.9 USB 2.0 - Device                                   |    |

| 3.10 USB 2.0 - HOST                                    |    |

| 3.11 I2C                                               |    |

| 3.12 SPI (SSP)                                         |    |

| 3.13 I2S (Inter-IC Sound)                              |    |

| 3.14 PWM (Pulse Width Modulation) / 16bit-Timers       |    |

| 3.15 JTAG                                              |    |

| 3.16 Keys / Keyboard                                   |    |

| 3.17 Analog/Digital Converter                          |    |

|                                                        |    |

| 3.18 Touch Screen Interface (TSI)                      |    |

| 3.20 Glyn Graphic Base Board & Glyn TFT Family Concept |    |

| 3.21 SD Host Controller                                |    |

|                                                        |    |

| 3.22 CMOS Camera Interface                             |    |

| 3.23 Melody/Alarm Generator                            |    |

| 3.24 Low Frequency Clock Output                        | 37 |

| 4.0 Pin Allocation SODIMM 144 Connector                | 38 |

| 5.0 Software Components                                | 44 |

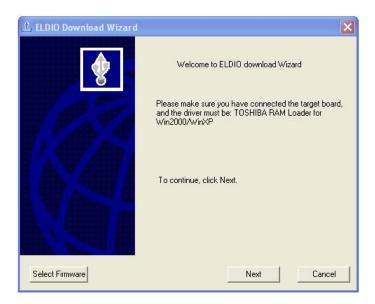

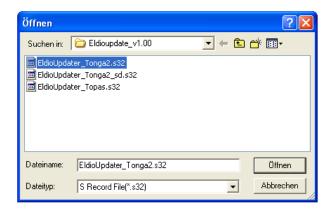

| 5.1 Basics - Data Transfer to TMPA900 CPU Board        | 44 |

| 5.1.1 ELDIO Download Wizard                            |    |

| 5.1.2 Basics – Installing J-Link Lite                  |    |

| 5.1.3 Basics - Installing a TFTP Server                |    |

|                                                        |    |

| 5.1.4 Basics - Working completely under Linux                             | 46        |

|---------------------------------------------------------------------------|-----------|

| 5.2 u-boot                                                                |           |

| 5.2.1 The Boot Process                                                    |           |

| 5.2.2 Flashing the u-boot                                                 | 49        |

| 5.2.2.1 Flashing the u-boot over JTAG                                     |           |

| 5.2.2.2 Update the u-boot via network (handle with care)                  | 50        |

| 5.2.2.3 U-boot - Environment Setup                                        |           |

| 5.2.2.4 IP and MAC Address Setup                                          | 51        |

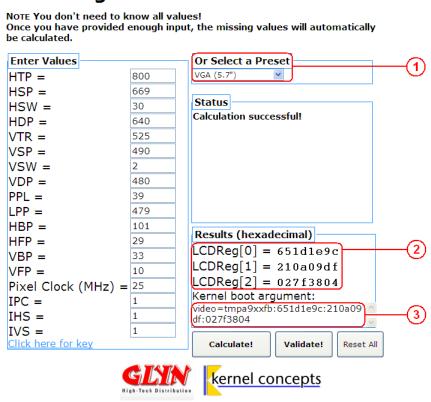

| 5.2.2.5 Configuration of the Display Parameters                           | 52        |

| 5.2.2.6 Configuration of the File System Type                             |           |

| 5.2.2.7 Splash Screen Support                                             |           |

| 5.2.2.8 Erase u-boot Environment.                                         |           |

| 5.2.2.9 u-boot - NFS Server Setup                                         |           |

| 5.2.2.10 More u-boot commands                                             |           |

| 5.2.2.11 What to do if the boot loader has been flashed incorrectly       |           |

| 5.3 Standard Application (IAR Compiler)                                   |           |

| 5.3.1 Debugging the Application (IAR Compiler)                            |           |

| 5.3.2 Make a Release for Flash (IAR Compiler)                             |           |

| 5.3.3 Flashing the Application (No Linux)                                 |           |

| 5.3.4 Getting Started with SEGGER Evaluation Software and IAR             |           |

|                                                                           |           |

| 6.0 Linux for TMPA900 CPU board                                           | 61        |

| 6.1 Major Components of a Linux System                                    |           |

| 6.2 Flashing the Linux Application                                        |           |

| 6.3 Flash Layout TMPA900-CPU-BOARD                                        | 63        |

| 6.4 Installation Linux Tool chain TMPA900 CPU board                       | 64        |

| 6.5 Linux Kernel Build                                                    |           |

| 6.5.1 Linux Kernel Source Tree                                            |           |

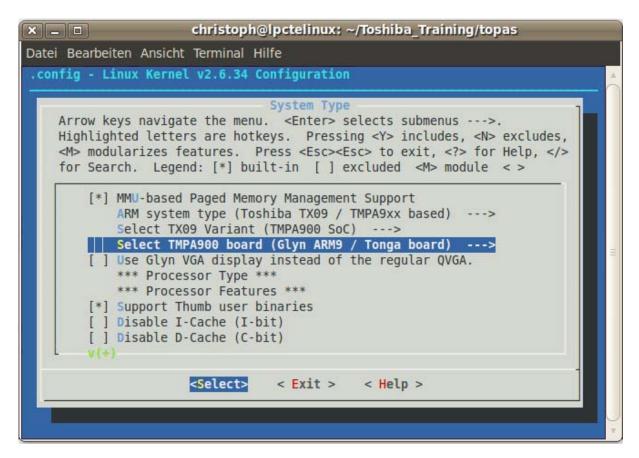

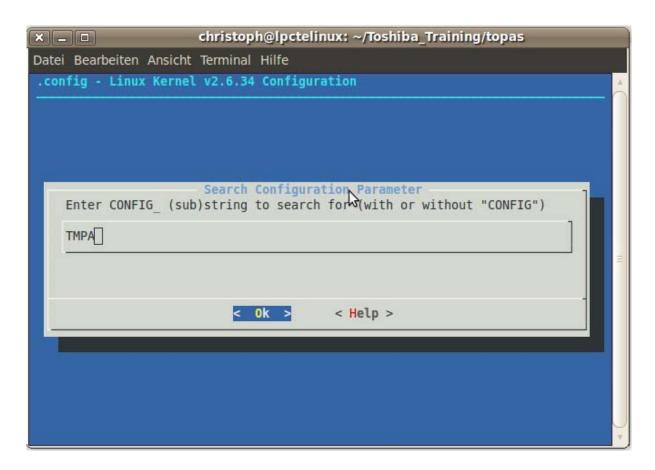

| 6.5.2 Linux Kernel Configuration                                          |           |

| 6.5.3 Compiling the Linux Kernel                                          |           |

| 6.5.4 Installing the Linux Kernel                                         |           |

| 6.6 Linux File System                                                     |           |

| 6.7 Small C-Examples under Linux                                          |           |

| 6.7.1 Linux "Hello World" Example                                         |           |

| 6.7.2 IO-Toggle – Example for an easy accesses to the peripherals         |           |

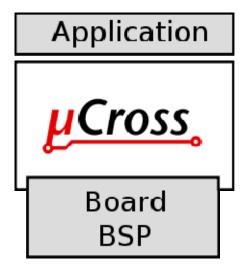

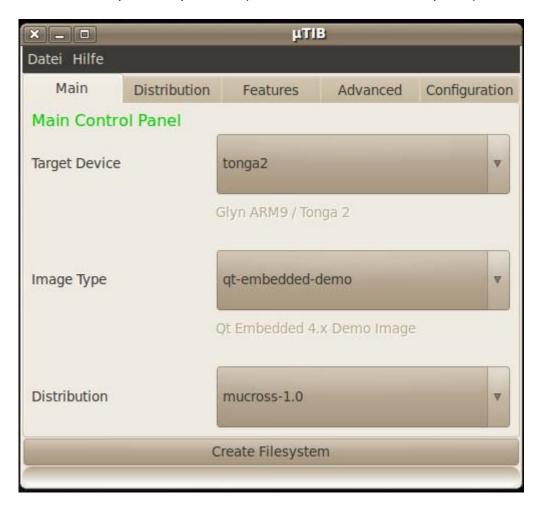

| 6.8 µCross – Linux Tool Package                                           |           |

| o.o poroco Emax room adhago                                               | , ,       |

| 7.0 Installing the Display with the Glyn Graphic Base Board               | 77        |

| 7.1 Other Resolutions/Other Timings – Calculation of the Display Settings |           |

| 7.1 Other Recording Other Thinings Calculation of the Dioplay Collings    | 7 0       |

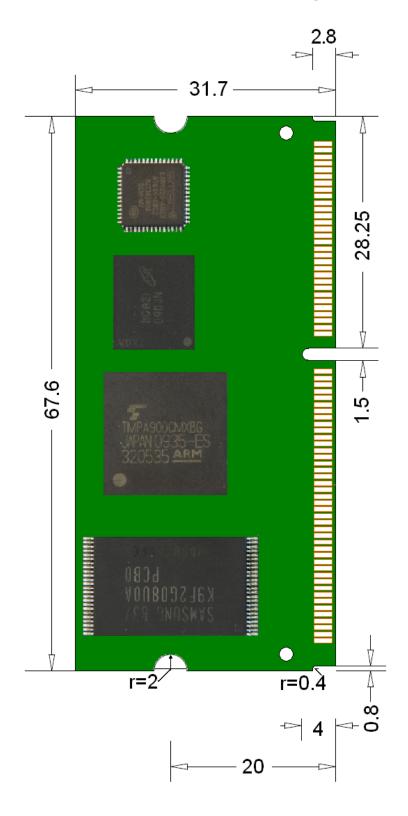

| 8.0 Mechanical Specifications (Formating)                                 | 79        |

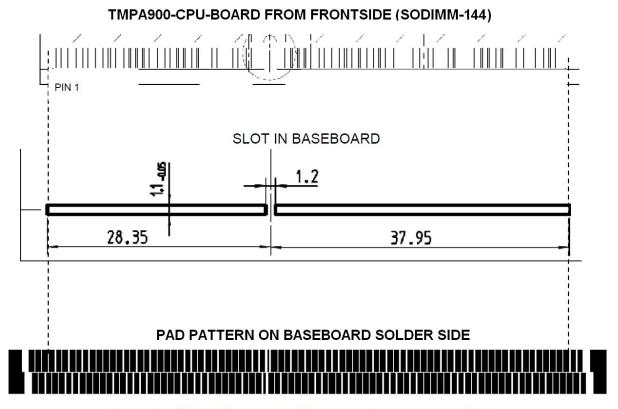

| 8.1 Soldering the TMPA900-CPU-Board – No Connector                        | 80        |

| o. I coldering the Tivil 7,000 of a Board Two confidence                  | 00        |

| Appendix A: Available u-boot Commands                                     | 81        |

| Appendix B: Ordering Information                                          |           |

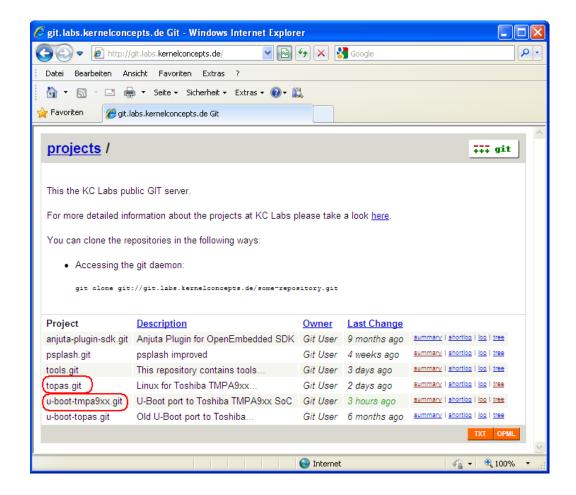

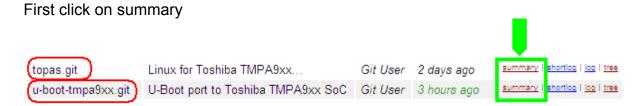

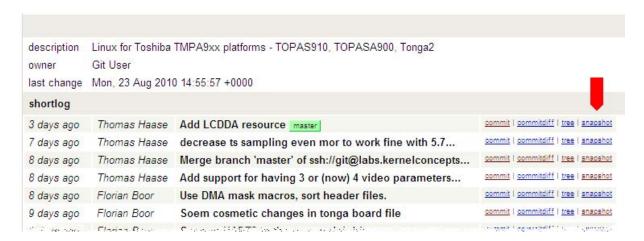

| Appendix C: KC Labs Public Git Server                                     | 03<br>1/2 |

| Appendix D: Literature and References                                     |           |

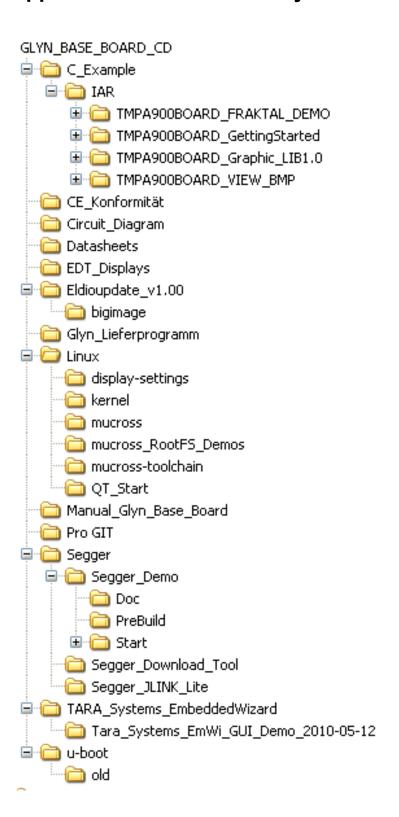

| Appendix E: CD file directory tree                                        |           |

| Appendix F: Contact Information                                           | وں<br>مم  |

| Appoint 1. Contact information                                            | 30        |

## 1.0 Revision List

| V0.1 | 30.12.2009 | CTE/OLE   | Document compilation                |

|------|------------|-----------|-------------------------------------|

| V0.2 | 13.01.2010 | CTE/OLE   | Revision Pin – Allocation           |

| V0.3 | 18.02.2010 | OLE       | Revision NAND FLASH                 |

| V0.4 | 07.04.2010 | OLE       | Manual for flashing the u-boot      |

| V0.5 | 08.04.2010 | OLE       | Manual for flashing the application |

| V1.0 | 09.04.2010 | CTE / HFR | Proof-reading                       |

| V1.1 | 14.04.2010 | OLE       | <b>Bootloader Correction</b>        |

| V1.2 | 21.04.2010 | OLE       | Correction Installation Linux Image |

| V1.3 | 18.05.2010 | OLE       | Corrections                         |

| V1.4 | 21.06.2010 | CTE       | New chapters 5.0, 6.5 and 7.1       |

| V1.5 | 05.08.2010 | CTE       | Completely revised manual           |

| V1.6 | 18.05.2010 | CTE       | New ELDIO Download Wizard           |

| V1.7 | 26.01.2011 | CTE       | Some Corrections, new chap. 6.7.2   |

|      |            |           |                                     |

## 1.1 Contacts

| Christoph Tenbergen | christoph.tenbergen@glyn.de | +49 2157 127-227 |

|---------------------|-----------------------------|------------------|

| Dominik Peuker      | dominik.peuker@glyn.de      | +49 6126 590-270 |

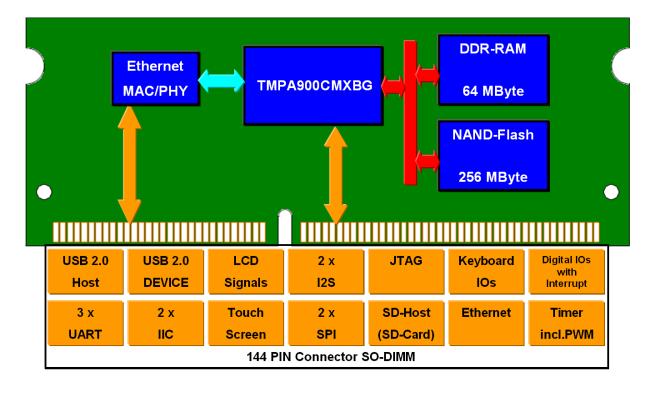

### 2.0 Summary

This report contains all important technical information regarding the TMPA900-CPU-board SODIMM module. Detailed information about the implemented parts can be found on the appropriate data sheets and a list with references is at the end of the document.

#### 2.1 Product Information TMPA900-CPU BOARD

Glyn's TMPA900-CPU board is a CPU module by Glyn GmbH & Co KG with Toshiba's TMPA900CMXBG ARM9 microcontroller. The integrated TFT controller enables RGB display driving with a resolution of 800x480 with integrated hardware acceleration. Dispensing with this acceleration enables up to 1024x1024. The module is a highly efficient and easy-to-integrate processor platform with graphic and video capability. The board is designed for mounting on a SODIMM socket which is also available from us – it is a SODIMM 144-pin socket used in the PC field. Additionally, it is also possible to dispense with the socket and solder the module for larger series sizes (further information available).

#### **System On-Module**

- Processor TMPA900CMXBG, 200 MHz

- RAM 64 MB DDRRAM

- ROM 256 MB NAND Flash

- Power supply single 3.0V to 3.6V

- Size SO-DIMM 144

- Temp.-range -20°C..85°C

#### **Key Features**

- 10/100Mbps Ethernet (MAC+PHY)

- High-speed USB 2.0 Device (480Mbps)

- Full-speed USB Host 2.0 (12Mbps)

- LCD controller

- CMOS camera interface

- Interfaces: UART, SD-CARD, I2C, PWM, Keypad, Digital Audio (I2S), 4/5 wire touch screen

The TMPA900-CPU-Board what comes with the Starterkit is pre-programmed with the UBoot and a Splashscreen.

There is no Linux-Kernel or other application programmed!

## 2.2 Energy Consumption at 3.3V (preliminary values)

|                   | mit et | hern |      | ohne Ethernet<br>(Initialisierung nicht<br>∨ollständig) |     |      |

|-------------------|--------|------|------|---------------------------------------------------------|-----|------|

| f (Fc = 200 Mhz)  | I/mA   |      | P/mW | I/mA P/mW                                               |     | P/mW |

| fc                |        | 328  | 1082 | 9 (3)                                                   | 174 | 574  |

| fc/2              |        | 267  | 881  | 8                                                       | 137 | 452  |

| fc/4<br>fc/8      |        | 239  | 789  | - 3                                                     | 119 | 393  |

| fc/8              |        | 225  | 743  | - 3                                                     | 110 | 363  |

| nach reset (halt) |        | 190  | 627  |                                                         | 75  | 248  |

## 2.3 Block Diagram

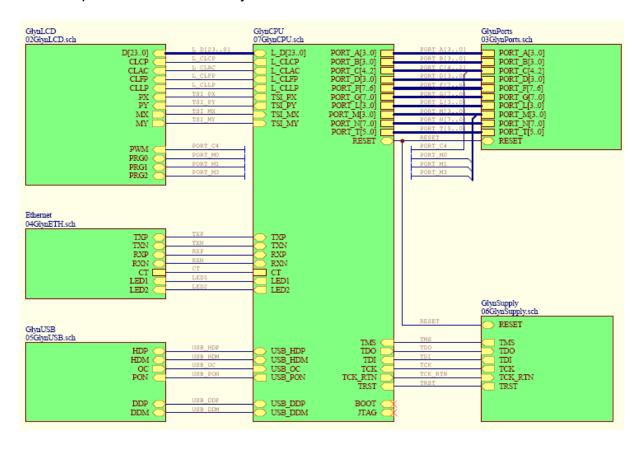

## 2.4 TMPA900 CPU Board Reference Circuitry

The complete reference circuitry can be found on the CD.

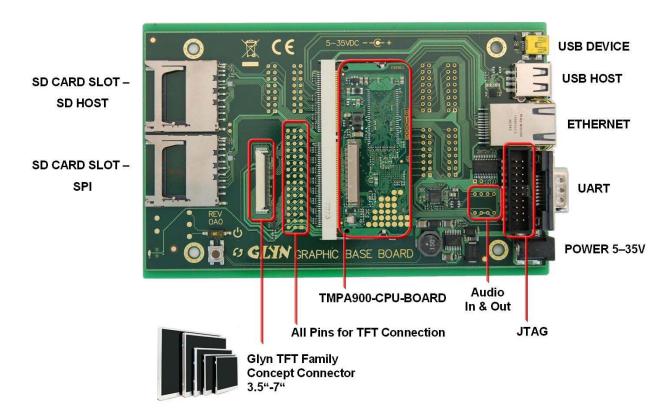

### 2.5 Glyn's Graphic Base Board

Glyn's Graphic Base Board is a platform in order to use the TMPA900-CPU board for a development. At the same time, it is also the reference design for including a TMPA900-CPU board. The plans and BOM list can be found on the CD in the file "Circuit\_Diagramm". Should layout data be required, this can also be provided against an NDA.

#### **Features**

- 144 PIN SODIMM connector

- Ethernet connector

- USB host connector

- USB device connector

- RS232

- WM8983 Audio Codec by Wolfson

- SD card sockets (SD-Host controller and via SPI)

- Glyn TFT concept connector für 3.5" 7" TFTs

- JTAG interface

- 100mm x 160mm

- Single power supply 5-35V

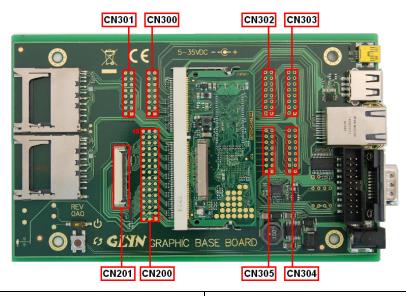

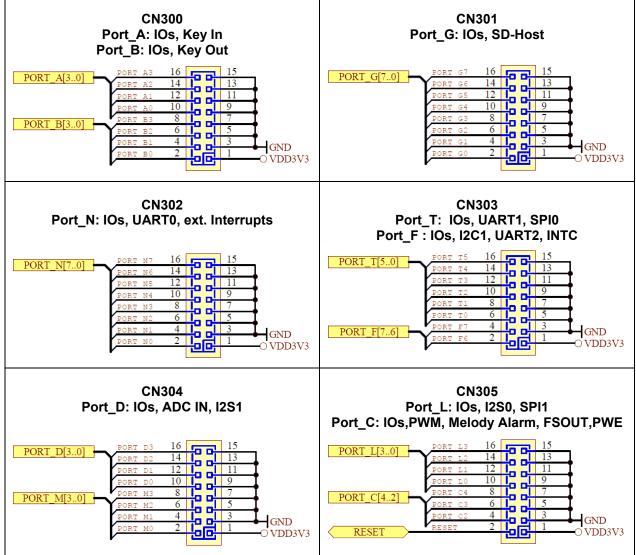

## 2.5.1 Glyn's Graphic Base Board Connectors

### 2.6 Instructions for use

The standard measures of precaution regarding touching and operating circuitry in low voltage ranges apply. Electrostatic discharging which may damage parts is to be avoided.

The board may be plugged in or out only when the supply voltage is switched off.

The parts used on the TMPA900 CPU board are specified for use between -20 and +85 Grad Celsius. The TMPA900 CPU board requires a DC voltage of  $3.3V \pm 0.2V$ .

### 3.0 Operational Description

This chapter provides a brief description of the module and its interfaces.

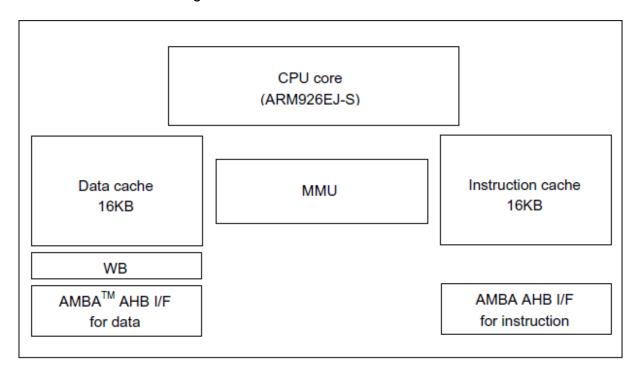

#### 3.1 CPU Core

Note that this document provides only an overview of the CPU block. Please contact ARM Holdings for operation details and refer to the TMPA900CMXBG manual. The TMPA900CM has a built-in 32-bit RISC processor ARM926EJ-S manufactured by ARM. The schematic diagram of the ARM926EJ-S core is shown below.

The TMPA900CM does not feature the functions shown below.

- 1. Coprocessor I/F

- 2. Embedded ICE RT

- 3. TCM I/F

- 4. ETM9TM I/F

### 3.2 Memory – Architecture

The TMPA900 is characterised by a multilayer AHB bus. The advantage over conventional architectures is the higher internal data throughput. To expand on this concept, there are two memory controllers for the external flash and RAM. The first is responsible for communication with NORFLASH, SRAM or SDRAM and the second is responsible for communication with NORFLASH, SRAM und DDR SDRAM. The external memory chips are each directly connected to one of these controllers.

The CSs of the external NAND flash are connected to pin D7/D8 on the TMPA900. The CSs of the external SRAM/DDRRAM are connected to pin K12 on the TMPA900

The TMPA900 has two operating modes – the external memory mode and the internal boot ROM mode which are specified by the external mode pins AM0 and AM1. Pin AM0 is set to high. Pin AM1 is connected to the expansion connector and marked BOOT (PIN132).

AM1 HIGH BOOT (start from internal Boot ROM)

AM1 LOW Start from external bus/memory (16-bit Bus)

Due to the internal structure of NAND memories, it is not possible to run a program directly from this memory. In fact, the user program code has to be copied from the NAND memory to the external RAM before starting the program. Access to the NAND flash takes place in a multiplexed 8-Bit mode.

The process has not been disclosed in detail. Should the customer require more information, we can request personalised documentation at Toshiba. This is free of charge.

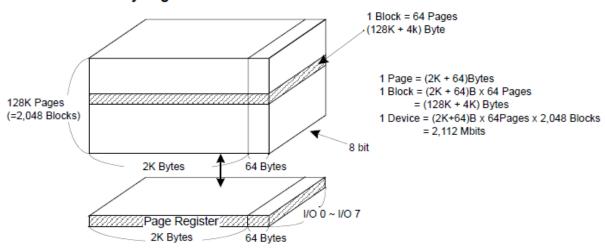

### 3.2.1 Nand Flash Memory - Unique Characteristics

- When it is erased, all bits are set to 1' (you will see 0xff on all bytes in a hexdump)

- You can change as many bits as you want to '0'

- You cannot set a bit back to '1' by using a regular write.

- You have to erase a whole erase block to do so

- The number of erase cycles per block is limited. Once you have reached the limit, some bits will not get back to 0xff. In the case of the in Samsung Flash K9F2G08 this is 100.000 guaranteed per-block erase cycles.

#### NAND page

A NAND page consists of a number of data bytes plus a number of out-of-band (OOB) bytes.

Only the data bytes are used for application data. The OOB bytes are used for

- Marking an erase block as bad (first or second page of erase block)

- Storing ECC (error correction codes)

- Storing file system specific information (JFFS2)

#### **NAND** erase block

An erase block consists of multiple pages. In K9F2G08 every erase block has 64 pages.

#### K9F2G08X0A Array Organization

#### **Problem: Bad Blocks**

NAND memory apparently gets shipped with blocks that are already bad. The vendor just marks those blocks as bad, thus resulting in higher yield and lower per-unit cost.

The flash contains four kinds of blocks (16kBytes):

- Factory default bad blocks

- Samsung marks the 6th OOB byte as non 0xFF in the first and/or second page in blocks that are bad

- Worn-out bad blocks

- Good blocks

- The first block. This block is guaranteed to not require error correction up to 1000 writes. This is needed as the initial boot code can't do ECC.

It is also guaranteed that a minimum of 2008 blocks (out of the total 2048) are good. This means up to 40 blocks (5.1MBytes) can be dead.

More about bad block handling in chapter 5.0 u-boot!

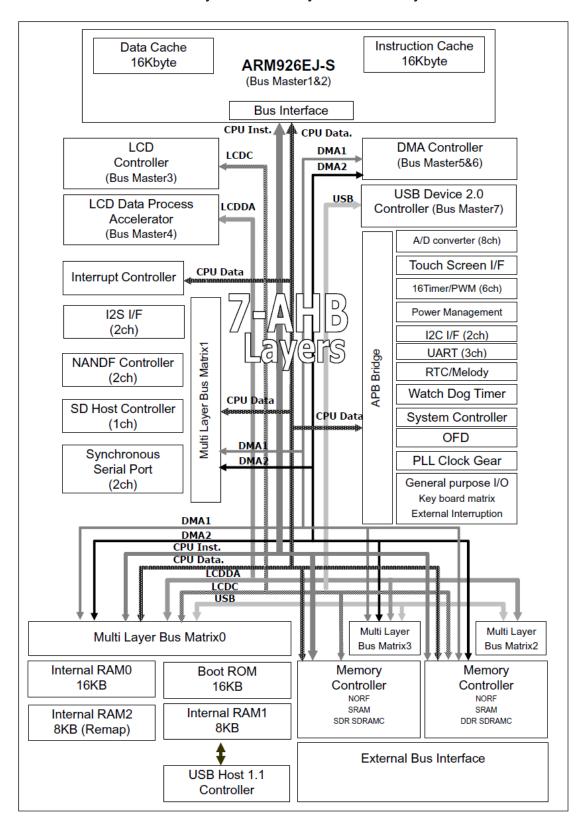

### 3.3 TMPA900CMXBG Block Diagram with Multilayer AHB

The TMP900CM uses a multilayer AHB bus system with 7 layers.

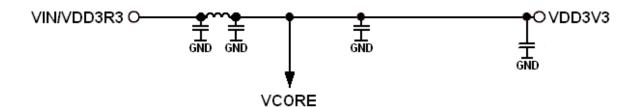

### 3.4 Power Supply

The parts used on the TMPA900 CPU board are specified for use between -20 and +85 Grad Celsius. The TMPA900 CPU board requires a DC voltage of  $3.3V \pm 0.2V$ .

The power is fed over the VDD3R3 pins. This power runs through some filters and is outputted over VDD3V3. External components which aren't supplied by the module should be supplied over VDD3V3.

The filters are switched between VIN/VDD3R3 and VDD3V3, so the voltage peak has the same effect on external components as on the module. The EMV critical part should be connected via the filters.

#### **Power Supply Pins VDD3R3:**

| Signal | PIN | Input/Output | Function Remarks          |

|--------|-----|--------------|---------------------------|

| VDD3R3 | 136 | Input        | DC IN complex 2.2V + 0.2V |

| VDD3R3 | 138 | Input        | DC-IN supply: 3.3V ± 0.2V |

| VDD3R3 | 140 | Input        |                           |

| VDD3R3 | 142 | Input        |                           |

#### **Power Output Pins VDD3V3:**

| Signal | PIN | Input/Output | Function Remarks       |

|--------|-----|--------------|------------------------|

| VDD3V3 | 3   | Output       | DO OUT VDD2D2 filessed |

| VDD3V3 | 4   | Output       | DC-OUT VDD3R3 filtered |

| VDD3V3 | 61  | Output       |                        |

| VDD3V3 | 62  | Output       |                        |

| VDD5W0 | 5   | -            | Not connected!         |

### **Ground Pins:**

| Signal | PIN | Input/Output | Function Remarks |

|--------|-----|--------------|------------------|

| GND    | 1   |              |                  |

| GND    | 2   |              | Ground           |

| GND    | 11  |              |                  |

| GND    | 12  |              |                  |

| GND    | 21  |              |                  |

| GND    | 22  |              |                  |

| GND    | 31  |              |                  |

| GND    | 32  |              |                  |

| GND    | 41  |              |                  |

| GND    | 42  |              |                  |

| GND    | 51  |              |                  |

| GND    | 52  |              |                  |

| GND    | 63  |              |                  |

| GND    | 64  |              |                  |

| GND    | 73  |              |                  |

| GND    | 74  |              |                  |

| GND    | 83  |              |                  |

| GND    | 84  |              |                  |

| GND    | 93  |              |                  |

| GND    | 94  |              |                  |

| GND    | 103 |              |                  |

| GND    | 104 |              |                  |

| GND    | 113 |              |                  |

| GND    | 114 |              |                  |

| GND    | 123 |              |                  |

| GND    | 124 |              |                  |

| GND    | 133 |              |                  |

| GND    | 134 |              |                  |

| GND    | 143 |              |                  |

| GND    | 144 |              |                  |

#### 3.5 RESET

Before resetting the TMPA900CM, make sure that the power supply voltage is within the operating range, oscillation from the internal oscillator is stable at at least 20 system clock cycles (0.8  $\mu$ s @ X1 = 25 MHz), and the RESET input pin is pulled Low. When the TMPA900CM is reset, the PLL stops, the PLL output is unselected, and the clock gear is set to TOP (1/1).

The system clock therefore operates at 25 MHz (X1 = 25 MHz).

| Signal | PIN | Input/Output | Function Remarks |

|--------|-----|--------------|------------------|

| RESET  | 112 | Input        | RESET            |

## 3.6 External power source control output

| Signal           | PIN | Input/Output | Function Remarks                                                                                                                                           |

|------------------|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWE<br>(PORT_C2) | 110 | Output       | This pin controls ON/OFF of the external power source. The "H" level is output during regular operations, and the "L" level is output during standby mode. |

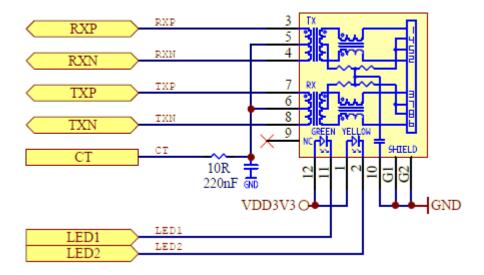

#### 3.7 Ethernet - Network Controller

There is an LAN9221i (Industrial Temperature Range) – Ethernet controller by SMSC integrated on the TMPA900-CPU board. This supports 10/100 MBit data communication. The Fifo – Select connection (Pin13) is connected to address A12 of the TMPA900. A 330Ohm series resistor has already been integrated for the network LEDs. Furthermore, the TXP, TXN, RXP and RXN are connected by a 490Ohm pull-up resistor. A MAC address has not been set; the firmware takes care of the assignment.

| Signal | PIN | Input/Output | Function Remarks                  |

|--------|-----|--------------|-----------------------------------|

| LED1   | 6   | Output       | LED1                              |

| LED2   | 8   | Output       | LED2                              |

| CT     | 10  | Output       | AVDD Output to Ethernet Magnetics |

| RXP    | 14  | Input        | Receive Positive                  |

| RXN    | 16  | Input        | Receive Negative                  |

| TXP    | 18  | Output       | Transmit Positive                 |

| TXN    | 20  | Output       | Transmit Negative                 |

Connection Example: RJ45 Female Connector on TMPA900-CPU-Board

## **3.8 UARTs**

The TMPA900-CPU-Board contains three UART channels. The feature of each channel is shown below.

|                     | UART 0                                | UART 1                   | UART 2             |  |  |  |

|---------------------|---------------------------------------|--------------------------|--------------------|--|--|--|

| Transmit FIFO       | 8-bit width / 16 location deep        |                          |                    |  |  |  |

| Receive FIFO        | 12-bit width /16location deep         |                          |                    |  |  |  |

| Transmit/Receive    | DATA bits: 5,6,7,8bits can be select  | cted                     |                    |  |  |  |

| data format         | PARITY: use / no use                  |                          |                    |  |  |  |

|                     | STOP bit:1bit / 2bits                 |                          |                    |  |  |  |

| FIFO ON/OFF         | ON (FIFO mode)/                       |                          |                    |  |  |  |

|                     | OFF (characters mode)                 |                          |                    |  |  |  |

| Interrupt           | (1) Combined interrupt factors are of | output to interrupt cont | roller.            |  |  |  |

|                     | (2) The permission of each interrup   |                          |                    |  |  |  |

| baud rate generator | Generates a common transmit a         | nd receive internal c    | lock from the UART |  |  |  |

|                     | internal reference clock input.       |                          |                    |  |  |  |

|                     | Supports baud rates of up to 6.15M    |                          |                    |  |  |  |

| DMA                 | Support                               | NO support               | support            |  |  |  |

| IrDA 1.0 Function   | (1) Max data rate:                    | N/A                      | N/A                |  |  |  |

|                     | 115.2kbps(half-duplex)                |                          |                    |  |  |  |

|                     | (2) support low power mode            |                          |                    |  |  |  |

| Control pins        | U0RXD                                 | U1RXD                    | U2RXD              |  |  |  |

|                     | U0TXD                                 | U1TXD                    | U2TXD              |  |  |  |

|                     | U0CTSn                                |                          |                    |  |  |  |

|                     | U0CTSn (Clear To Send)                |                          |                    |  |  |  |

|                     | U0DCDn (Data Carrier Detect)          |                          |                    |  |  |  |

|                     | U0DSRn (Data Set Ready)               |                          |                    |  |  |  |

|                     | U0RIn (Ring Indicator)                |                          |                    |  |  |  |

|                     | U0RTSn(Request To Send)               |                          |                    |  |  |  |

|                     | U0DTRn (Data Terminal Ready)          | 110                      | N1/A               |  |  |  |

| Hardware flow       | RTS support                           | NC                       | N/A                |  |  |  |

| control             | CTS support                           |                          |                    |  |  |  |

#### **UART0:**

| Signal               | PIN | Input/Output | Function Remarks                                    |

|----------------------|-----|--------------|-----------------------------------------------------|

| U0RTSn<br>(PORT_N7)  | 24  | Output       | Output modem control line RTD(Request To Send)      |

| U0DTRn<br>(PORT_N6)  | 26  | Output       | Output modem control line DTR (Data Terminal Ready) |

| U0RIn<br>(PORT_N5)   | 28  | Input        | Modem status signal RI (Ring Indicator)             |

| U0DSRIn<br>(PORT_N4) | 30  | Input        | Modem status signal DSR (Data Set Ready)            |

| U0DCDn<br>(PORT_N3)  | 34  | Input        | Modem status signal DCD (Data Carrier Detect)       |

| U0CTSn<br>(PORT_N2)  | 36  | Input        | UART0 data can be transmitted (Clear to send)       |

| U0RXD<br>(PORT_N1)   | 38  | Input        | UART0 receive data                                  |

| U0TXD<br>(PORT_N0)   | 40  | Output       | UART0 transmission data                             |

#### **UART1:**

| Signal             | PIN | Input/Output | Function Remarks        |

|--------------------|-----|--------------|-------------------------|

| U1RXD<br>(PORT_T5) | 44  | Input        | UART1 receive data      |

| U1TXD<br>(PORT_T4) | 46  | Output       | UART1 transmission data |

#### **UART2:**

| Signal             | PIN | Input/Output | Function Remarks        |

|--------------------|-----|--------------|-------------------------|

| U2RXD<br>(PORT_F7) | 58  | Input        | UART2 receive data      |

| U2TXD<br>(PORT_F6) | 60  | Output       | UART2 transmission data |

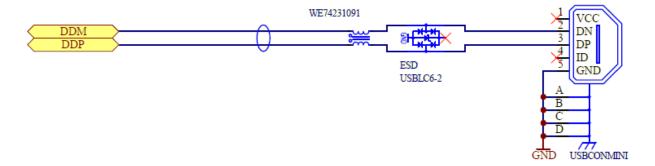

#### 3.9 USB 2.0 - Device

#### Features:

- Conforms with universal serial bus specification Rev. 2.0

- Supports both high-speed and full-speed (low-speed is not supported).

- Supports Chirp.

- USB protocol processing

- Detects SOF/USB\_RESET/SUSPEND/RESUME.

- Generates and checks packet IDs.

- Generates and checks data synchronization bits (DATA0/DATA1/DATA2/MDATA).

- Checks CRC5, generates and checks CRC16.

- Supports PING.

- Supports 4 transfer modes (Control/Interrupt/Bulk/Isochronous).

- Supports 4 endpoints:

- o Endpoint 0: Control 64 bytes × 1 FIFO

- o Endpoint 1: Bulk (IN) 512 bytes × 2 FIFOs

- o Endpoint 2: Bulk (OUT) 512 bytes × 2 FIFOs

- Endpoint 3: Interrupt (IN) 64 bytes × 1 FIFO

- Supports dual packet mode (except for Endpoint 0).

- Interrupt source signal to interrupt controller: INTS[21]

| Signal  | PIN | Input/Output | Function Remarks    |

|---------|-----|--------------|---------------------|

| USB_DDP | 17  | Input/Output | USB Device pin (D+) |

| USB_DDM | 19  | Input/Output | USB Device pin (D-) |

#### Connection Example: MINI USB on the TMPA900-CPU-Board

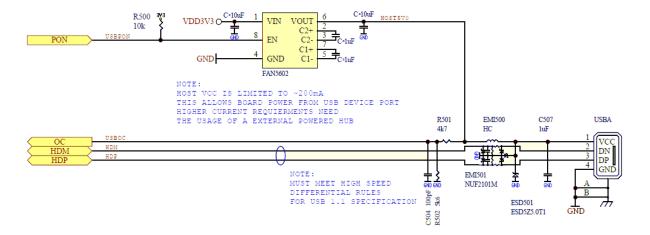

#### 3.10 USB 2.0 - HOST

The USB host controller (USBHC) is compliant with USB specification revision 2.0 and the open HCl specification release 1.0a and supports USB transfers at 12 Mbps (full-speed). The USBHC is connected to the multi-layer bus system via on-chip SRAM.

#### Features:

- Supports full-speed (12 Mbps) USB devices. But doesn't supports low-speed (1.5Mbps)

- Supports control, bulk, interrupt and isochronous transfers.

- Contains two 16-byte FIFO buffers (IN and OUT) in the bus bridge logic for connecting with the CPU, allowing a maximum of 16-byte burst transfers.

- Supports data transfers between the FIFO buffers in the bus bridge logic and the on-chip SRAM.

| Signal  | PIN | Input/Output | Function Remarks                 |

|---------|-----|--------------|----------------------------------|

| USB_OC  | 7   | Input        | Over current detect for USB host |

| USB_PON | 9   | Output       | Power on enable for USB host     |

| USB_HDP | 13  | Input/Output | USB host data (D+)               |

| USB_HDM | 15  | Input/Output | USB host data (D-)               |

#### Connection Example: USB host type A on the TMPA900 CPU board

#### 3.11 I2C

This module operates in I2C bus mode and is compliant with the typical I2C bus standard (Philips specifications).

#### Features:

- Contains two channels (ch0 and ch1).

- Allows selection between master and slave.

- Allows selection between transmission and reception.

- Supports multiple masters (arbitration, clock synchronization recognition).

- Supports standard mode and fast mode (fastest baud rate in master mode: 89.91 kHz andn357.14 kHz, respectively, at fPCLK = 100 MHz)

- Supports the addressing format of 7 bits only.

- Supports transfer data sizes of 1 to 8 bits.

- Provides one transfer (transmission or reception) complete interrupt (levelsensitive).

- Can enable or disable interrupts. (Interrupt source for I2C ch0: INTS[6], Interrupt source for I2C ch1: INTS[7])

#### **I2C Channel 0:**

Normally used for USB host

| Signal              | PIN | Input/Output | Function Remarks |

|---------------------|-----|--------------|------------------|

| I2C0CL<br>(USB_OC)  | 7   | Input/Output | I2C clock I/O    |

| I2C0DA<br>(USB_PON) | 9   | Input/Output | I2C data I/O     |

#### I2C Channel 1:

| Signal              | PIN | Input/Output | Function Remarks |

|---------------------|-----|--------------|------------------|

| I2C1CL<br>(Port_F6) | 60  | Input/Output | I2C clock I/O    |

| I2C1DA<br>(Port_F7) | 58  | Input/Output | I2C data I/O     |

### 3.12 SPI (SSP)

#### Features:

- Contains two channels (ch0 and ch1).

- Communication protocol includes SPI: 3 types

- Master/ slave mode support

- Transmit FIFOs 16-bit wide, 8 locations deep

- Receive FIFOs 16-bit wide, 8 locations deep

- Transmit/Receive data size 4 to 16 bits

- Interrupt type:

- o Transmits interrupt

- o Receives interrupt

- o Receives overrun interrupt

- Timeout interrupt

- Baud rate master mode: fPCLK/2 (Max 20 Mbps)

- Slave mode: fPCLK/12 (Max 8.33 Mbps)

- DMA Support

- Internal loop back test mode available

#### SPI (SSP) Channel 0:

| Signal    | PIN | Input/Output | Function Remarks         |

|-----------|-----|--------------|--------------------------|

| SP0D      | 48  | Input        | Data input pin for SSP0  |

| (Port_T3) |     |              |                          |

| SP0DO     | 50  | Output       | Data output pin for SSP0 |

| (Port_T2) |     |              |                          |

| SP0CLK    | 54  | Input/Output | Clock pin for SSP0       |

| (Port_T1) |     |              | ·                        |

| SP0FSS    | 56  | Input/Output | FSS pin for SSP0         |

| (Port_T0) |     |              | ·                        |

#### SPI (SSP) Channel 1:

| Signal              | PIN | Input/Output | Function Remarks         |

|---------------------|-----|--------------|--------------------------|

| SP1DI<br>(Port_L3)  | 96  | Input        | Data input pin for SSP1  |

| SP1DO<br>(Port_L2)  | 98  | Output       | Data output pin for SSP1 |

| SP1CLK<br>(Port_L1) | 100 | Input/Output | Clock pin for SSP1       |

| SP1FSS<br>(Port_L0) | 102 | Input/Output | FSS pin for SSP1         |

## 3.13 I2S (Inter-IC Sound)

The TMPA900CM contains a serial input/output circuit compliant with the I2S format. By connecting an external audio LSI, such as an AD converter or DA converter, the I2S interface can support the implementation of a digital audio system.

#### Features:

|                  | Channel 0                                                  | Channel 1                |  |  |

|------------------|------------------------------------------------------------|--------------------------|--|--|

| Transmit/Receive | Receive only                                               | Transmit only            |  |  |

| Modes            | Receive master mode                                        | Transmit master mode     |  |  |

|                  | Receive slave mode                                         | Transmit slave mode      |  |  |

|                  | Full-duple                                                 | x master mode            |  |  |

|                  | Full-duple                                                 | ex slave mode            |  |  |

|                  | Clock th                                                   | nrough mode              |  |  |

| Data formats     | (1) I2S format-compliant                                   |                          |  |  |

|                  | (2) Stereo/monaural                                        |                          |  |  |

|                  | (3) MSB first/LSB first selectable                         |                          |  |  |

|                  | (4) Left-justified supported (synchronous to WS, no delay) |                          |  |  |

| FIFO buffer      | 2 × 8 words 2 × 8 words                                    |                          |  |  |

| Data length      | 16 bits only 16 bits only                                  |                          |  |  |

| Interrupts       | FIFO overflow interrupt FIFO overflow interrup             |                          |  |  |

|                  | FIFO underflow interrupt                                   | FIFO underflow interrupt |  |  |

#### I2S Channel 0:

| Signal                | PIN | Input/Output | Function Remarks                             |

|-----------------------|-----|--------------|----------------------------------------------|

| I2S0MCLK<br>(Port_L3) | 96  | Output       | I2S0 master clock output for receive circuit |

| I2S0DATI<br>(Port_L2) | 98  | Input        | I2S0 receive serial data input               |

| I2S0CLK<br>(Port_L1)  | 100 | Input/Output | I2S0 serial clock Input/output               |

| I2S0WS<br>(Port_L0)   | 102 | Input/Output | I2S0 word select Input/output                |

#### **I2S Channel 1:**

| Signal    | PIN | Input/Output | Function Remarks                             |

|-----------|-----|--------------|----------------------------------------------|

| I2S1MCLK  | 86  | Output       | I2S1 master clock output for receive circuit |

| (Port_M3) |     |              |                                              |

| I2S2DATO  | 88  | Output       | I2S1 transmission serial data output         |

| (Port_M2) |     |              |                                              |

| I2S3CLK   | 90  | Input/Output | I2S1 serial clock Input/output               |

| (Port_M1) |     |              |                                              |

| I2S4WS    | 92  | Input/Output | I2S1 word select Input/output                |

| (Port_M0) |     |              | ·                                            |

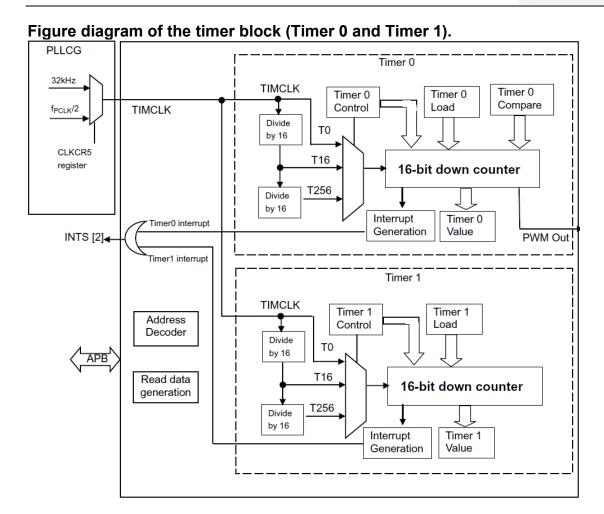

### 3.14 PWM (Pulse Width Modulation) / 16bit-Timers

The TMPA900 CPU board contains six cannels of 16-bit timers. Two of them, timer 0 and timer 2 support PWM (Pulse Width Modulation) output.

- 1) Free-running mode

- 2) Periodic timer mode

- 3) PWM function support

The circuit consists of three blocks, each associated with two channels. Of the three blocks, block 1 and block 2 support PWM (Pulse Width Modulation) output.

|                            | Block 1              |        | Bloo                 | ck 2   | Block 3 |        |

|----------------------------|----------------------|--------|----------------------|--------|---------|--------|

|                            | Timer0               | Timer1 | Timer2               | Timer3 | Timer4  | Timer5 |

| Free-Running               | •                    | •      | •                    | •      | •       | •      |

| Periodic Timer             | •                    | •      | •                    | •      | •       | •      |

| PWM                        | •                    | N/A    | •                    | N/A    | N/A     | A      |

|                            | PWM0OUT<br>(Port_C3) | х      | PWM2OUT<br>(Port_C4) | х      | х       | х      |

| Interrupt<br>Source Signal | INTS[2]              |        | INT                  | S[3]   | INTS    | 5[4]   |

| Signal               | PIN | Input/Output | Function Remarks        |

|----------------------|-----|--------------|-------------------------|

| PWM0OUT<br>(Port_C3) | 108 | Output       | Timer 0 PWM output port |

| PWM2OUT<br>(Port_C4) | 106 | Output       | Timer 2 PWM output port |

Each timer block, containing two channels of timer circuits, comprises two programmable, 16-bit free-running decrement counters. The TIMCLK input is used for counter operation. This clock can be selected from the internal system clock divided by two (fPCLK/2) and fs (32.768 kHz).

### **3.15 JTAG**

The TMPA900CMXBG provides a boundary scan interface that is compatible with Joint Test Action Group (JTAG) specifications and uses the industrial standard JTAG protocol (IEEE Standard 1149.1•1990 < Includes IEEE Standard 1449.1a•1993 >).

| Signal  | PIN | Input/Output | Function Remarks                                                                                              |

|---------|-----|--------------|---------------------------------------------------------------------------------------------------------------|

| TDO     | 116 | Output       | Data output pin for JTAG                                                                                      |

| TCK RTN | 118 | Output       | JTAG test feedback serial clock output                                                                        |

| TCK     | 120 | Input        | Clock pin for JTAG                                                                                            |

| TMS     | 122 | Input        | Data for JTAG                                                                                                 |

| TDI     | 126 | Input        | Data input pin for JTAG                                                                                       |

| TRST    | 128 | Input        | RESET pin for JTAG                                                                                            |

| JTAG    | 130 | Input        | Boundary scan switching pin, ICE/JTAG test select input (compatible with the Enable signal) -> 0: ICE 1: JTAG |

| BOOT    | 132 | Input        | AM1 Pin                                                                                                       |

### 3.16 Keys / Keyboard

Port A can be used not only as a general-purpose input pin with pull up, but also as a key input pin. By enabling interrupts, Port A is used as key input pins (KI3-KI0). Port A can be used without pull up.

Port B can be used not only as general-purpose output pins, but also as key output pins. By enabling open-drain output, Port B is used as key output (KO3-KO0).

| Signal        | PIN | Input/Output | Function Remarks                                                                 |  |

|---------------|-----|--------------|----------------------------------------------------------------------------------|--|

| Port A0 (KI0) | 29  | Input        | Port A0 to A2: Input ports                                                       |  |

| Port A1 (KI1) | 27  | Input        | Port A0 to A3: Input ports  Key input KI0 to KI3: Pins for key-on wake up 0 to 3 |  |

| Port A2 (KI2) | 25  | Input        | (with Schmitt input and pull-up resistor)                                        |  |

| Port A3 (KI3) | 23  | Input        |                                                                                  |  |

| Port B0 (KO0) | 33  | Output       | Port PO to P2: Output ports                                                      |  |

| Port B1 (KO1) | 35  | Output       | Port B0 to B3: Output ports  Key output KO0 zp KO3: Key out pins 0 to 3          |  |

| Port B2 (KO2) | 37  | Output       | (open-drain can be set)                                                          |  |

| Port B3 (KO3) | 39  | Output       |                                                                                  |  |

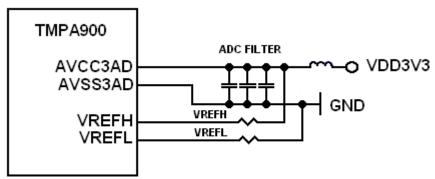

## 3.17 Analog/Digital Converter

A 10-bit serial conversion analog/digital converter (AD converter) with eight channels of analog input is built-in. Four channels (AN4-AN7) are normally used for touch screen interface.

Power Supply of ADC:

| Signal    | PIN | Input/Output | Function Remarks                                 |

|-----------|-----|--------------|--------------------------------------------------|

| AN0       | 82  | Input        |                                                  |

| (Port_D0) |     |              | Port D0 to D3: Input ports                       |

| AN1       | 80  | Input        | Analog input AN0 to AN3: AD Converter Input Pins |

| (Port_D1) |     |              |                                                  |

| AN2       | 78  | Input        |                                                  |

| (Port_D2) |     |              |                                                  |

| AN3       | 76  | Input        |                                                  |

| (Port_D3) |     |              |                                                  |

#### Pins normally used for Touch Screen Interface

| Signal   | PIN | Input/Output | Function Remarks                                 |

|----------|-----|--------------|--------------------------------------------------|

| AN7      | 65  | Output       |                                                  |

| (TSI_PY) |     |              | Port D4 to D7: Input ports                       |

| AN6      | 67  | Output       | Analog input AN4 to AN7: AD Converter Input Pins |

| (TSI_PX) |     |              |                                                  |

| AN5      | 69  | Output       |                                                  |

| (TSI_MY) |     |              |                                                  |

| AN4      | 71  | Output       |                                                  |

| (TSI_MX) |     |              |                                                  |

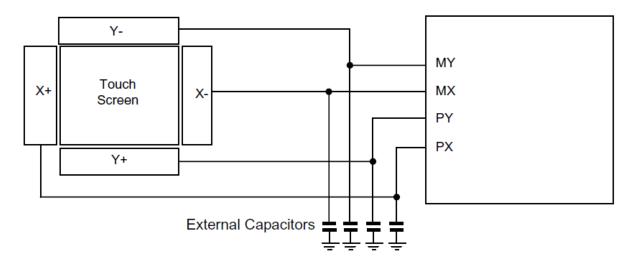

## 3.18 Touch Screen Interface (TSI)

An interface for a 4-terminal resistor network touch screen is built-in. The TSI easily supports two procedures: touch detection and X/Y position measurement. Each procedure is performed.

### TMPA900\_CPU\_BOARD

| Signal                  | PIN | Input/Output | Function Remarks                          |

|-------------------------|-----|--------------|-------------------------------------------|

| TSI_PY<br>(Port_D7/AN7) | 65  | Output       | Y-plus: Y-connecting pin for touch panel  |

| TSI_PX<br>(Port_D6/AN6) | 67  | Output       | X-plus: X-connecting pin for touch panel  |

| TSI_MY<br>(Port_D5/AN5) | 69  | Output       | Y-minus: Y-connecting pin for touch panel |

| TSI_MX<br>(Port_D4/AN4) | 71  | Output       | X-minus: X-connecting pin for touch panel |

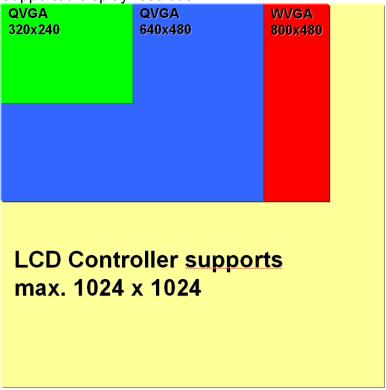

## 3.19 LCD Controller (LCDC)

SUPPORTED DISPLAY COLORS & DISPLAY RESOLUTION Display colours: from 256 to 16 million:

| Data bus width | RGB      | Display colours |

|----------------|----------|-----------------|

| 24 bit         | R8:G8:B8 | 16 million      |

| 18 bit         | R6:G6:B6 | 262 144         |

| 16 bit         | R5:G6:B5 | 65 536          |

| 12 bit         | R4:G4:B4 | 4 096           |

| 8 bit          | R3:G3:B2 | 256             |

Supported display resolution:

Up to WVGA with LCD data process accelerator:

- Scaling function (expansion/reduction)

- Filter function (bi-cubic convolution)

- Image blending function (font blending)

Up to 1024 x 1024 without accelerator and limited colour depth.

## **LCD Interface Signals:**

| Signal | PIN | Input/Output | Function Remarks                       |

|--------|-----|--------------|----------------------------------------|

| L_CLLP | 116 | Output       | Data output pin for JTAG               |

| L_CLFP | 118 | Output       | JTAG test feedback serial clock output |

| L_CLAC | 120 | Input        | Clock pin for JTAG                     |

| L_CLCP | 122 | Input        | Data for JTAG                          |

| Signal | PIN | Input/Output | Function Remarks     |

|--------|-----|--------------|----------------------|

| L_D0   | 141 | Output       | LCD data driver line |

| L_D1   | 139 | Output       | LCD data driver line |

| L_D2   | 137 | Output       | LCD data driver line |

| L_D3   | 135 | Output       | LCD data driver line |

| L_D4   | 131 | Output       | LCD data driver line |

| L_D5   | 129 | Output       | LCD data driver line |

| L_D6   | 127 | Output       | LCD data driver line |

| L_D7   | 125 | Output       | LCD data driver line |

| L_D8   | 121 | Output       | LCD data driver line |

| L_D9   | 119 | Output       | LCD data driver line |

| L_D10  | 117 | Output       | LCD data driver line |

| L_D11  | 115 | Output       | LCD data driver line |

| L_D12  | 111 | Output       | LCD data driver line |

| L_D13  | 109 | Output       | LCD data driver line |

| L_D14  | 107 | Output       | LCD data driver line |

| L_D15  | 105 | Output       | LCD data driver line |

| L_D16  | 101 | Output       | LCD data driver line |

| L_D17  | 99  | Output       | LCD data driver line |

| L_D18  | 97  | Output       | LCD data driver line |

| L_D19  | 95  | Output       | LCD data driver line |

| L_D20  | 91  | Output       | LCD data driver line |

| L_D21  | 89  | Output       | LCD data driver line |

| L_D22  | 87  | Output       | LCD data driver line |

| L_D23  | 85  | Output       | LCD data driver line |

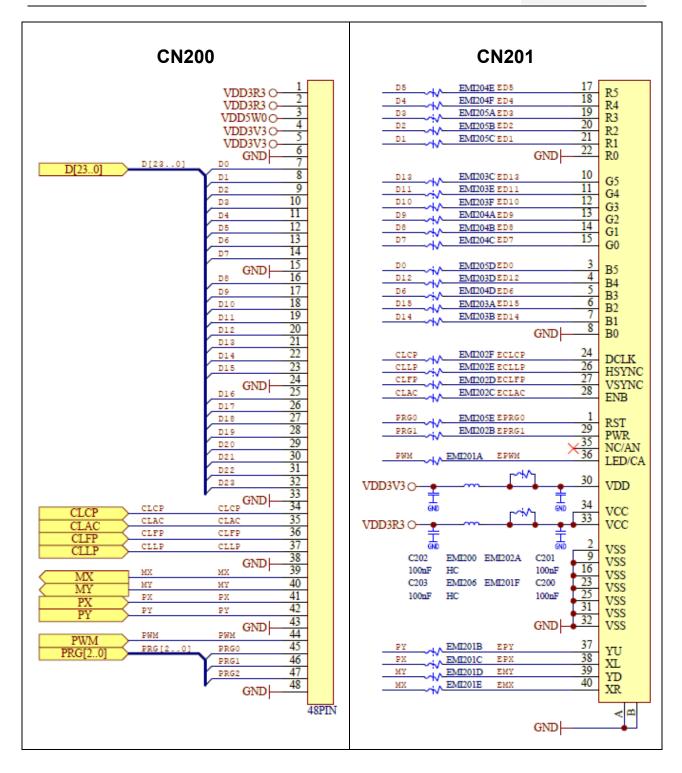

### 3.20 Glyn Graphic Base Board & Glyn TFT Family Concept

#### The Concept

Our objective was to offer a number of TFTs that . . .

- 1) are compatible with each other,

- 2) provide a modern interface and

- 3) have long-term availability.

In close collaboration with our partner EDT (Emerging Display Technologies), we have selected a number of TFTs that have been modified according to your needs. A PCB on the back of the display provides important functionalities as well as a common interface.

The family concept displays can be connected to the graphic base board (starter kit) directly. All display signals are lead through the SODIMM slot.

7.0" - 5.7" - 5.0" - 4.3" - 3.5"

| Part number         | Size | Resolution | Dimensions       |

|---------------------|------|------------|------------------|

| G-ET0350G0DM6 (DH6) | 3.5" | 320 x 240  | 76.8 x 63.8 mm   |

| G-ET0430G0DM6 (DH6) | 4.3" | 480 x 272  | 105.5 x 67.2 mm  |

| G-ET0500G0DM6 (DH6) | 5.0" | 800 x 480  | 118.5 x 77.6 mm  |

| G-ETQ570G0DM6 (DH6) | 5.7" | 320 x 240  | 124.7 x 100 mm   |

| G-ETQ570G2DM6 (DH6) | 5.7" | 320 x 240  | 142.1 x 100 mm * |

| G-ETV570G0DMU (DHU) | 5.7" | 640 x 480  | 124.7 x 100 mm   |

| G-ETV570G2DMU (DHU) | 5.7" | 640 x 480  | 142.1 x 100 mm * |

| G-ET0700G0DM6 (DH6) | 7.0" | 800 x 480  | 166 x 105.4 mm   |

DH6/DHU = with touch panel

\* with mounting lugs

## Pin Assignment of TFT Family Concept

| 1  | NC or /RESET | Hardware Reset (no Reset for 4.3" and 7.0")                                   |

|----|--------------|-------------------------------------------------------------------------------|

| 2  | Vss          | Ground (connected to metal houseing)                                          |

| 3  | B5           | Blue Data Bit 5                                                               |

| 4  | B4           | Blue Data Bit 4                                                               |

| 5  | В3           | Blue Data Bit 3                                                               |

| 6  | B2           | Blue Data Bit 2                                                               |

| 7  | B1           | Blue Data Bit 1                                                               |

| 8  | В0           | Blue Data Bit 0                                                               |

| 9  | Vss          | Ground (connected to metal houseing)                                          |

| 10 | G5           | Green Data Bit 5                                                              |

| 11 | G4           | Green Data Bit 4                                                              |

| 12 | G3           | Green Data Bit 3                                                              |

| 13 | G2           | Green Data Bit 2                                                              |

| 14 | G1           | Green Data Bit 1                                                              |

| 15 | G0           | Green Data Bit 0                                                              |

| 16 | Vss          | Ground (connected to metal houseing)                                          |

| 17 | R5           | Red Data Bit 5                                                                |

| 18 | R4           | Red Data Bit 4                                                                |

| 19 | R3           | Red Data Bit 3                                                                |

| 20 | R2           | Red Data Bit 2                                                                |

| 21 | R1           | Red Data Bit 1                                                                |

| 22 | R0           | Red Data Bit 0                                                                |

| 23 | Vss          | Ground (connected to metal houseing)                                          |

| 24 | DCLK         | Dot Clock                                                                     |

| 25 | Vss          | Ground (connected to metal houseing)                                          |

| 26 | HSYNC        | Horizontal Sync Input                                                         |

| 27 | VSYNC        | Vertical Sync Input                                                           |

| 28 | ENB          | Data Enable Input                                                             |

| 29 | PWCTRL       | LED driver shut down (on 5.7" it is a complete shut down of internal circuit) |

| 30 | VDD          | Power supply for digital circuit                                              |

| 31 | Vss          | Ground (connected to metal housing)                                           |

| 32 | Vss          | Ground (connected to metal housing)                                           |

| 33 | Vcc          | Power supply for Vcom driver circuit (internal voltages)                      |

| 34 | Vcc          | Power supply for Vcom driver circuit (internal voltages)                      |

| 35 | NC           | Not connected / This becomes LED anode, when jumper setting is changed        |

| 36 | LEDCTRL      | Brightness control (or LED cathode, when jumper setting is changed)           |

| 37 | YU           | Touch (Top)                                                                   |

| 38 | XL           | Touch (Left)                                                                  |

| 39 | YD           | Touch (Bottom)                                                                |

| 40 | XR           | Touch (Right)                                                                 |

#### 3.21 SD Host Controller

#### Features:

- Data transmission/reception in frame units

- Error check: CRC7 (for commands), CRC16 (for Data)

- Synchronous method: bit synchronous by SDCLK

- SD memory/IO card interface: COMMAND (1bit), Data (4 bits), INT (1bit)

- Multiple port support: 1 card

- 512byte ×2 data buffer: 256words×16bits×2

- Card detect support (SDCxCD or SDCxDAT3)

- Data write protect support

- Detected below Status error

- SDbuffer underflow /overflow

- o timeout (response, other

- o END error, CRC error, CMD error

- Recognizes the various response frame formats through the register settings

- The SD\_CLK cycle division ratio can be set from fPCLK/2 to fPCLK/512

- The transfer data length can be set from either 1byte to 512byte

- Sector counter for multiple read/write operation (read: single read only)

- Buffer status mode transfer support

This product contains an SD host controller for controlling SD cards. To use the SD host controller, you need to join the SD Association. Please also note that a non-disclosure agreement must be signed with us before the detailed specifications of the SD host controller can be disclosed. For details, please contact us.

| Signal                | PIN | Input/Output | Function Remarks                               |

|-----------------------|-----|--------------|------------------------------------------------|

| SDC0DAT0<br>(Port_G0) | 59  | Input/Output |                                                |

| SDC0DAT1<br>(Port_G1) | 57  | Input/Output | SDC0DAT0 to SDC0DAT3: Data I/O pin for SD card |

| SDC0DAT2<br>(Port_G2) | 55  | Input/Output |                                                |

| SDC0DAT3<br>(Port_G3) | 53  | Input/Output |                                                |

| SDC0CMD<br>(Port_G4)  | 49  | Input/Output | Command I/O pin for SD card                    |

| SDC0WP<br>(Port_G5)   | 47  | Input        | Write-protect input pin for SD card            |

| SDC0CD<br>(Port_G6)   | 45  | Input        | Card detection input pin for SD card           |

| SDC0CLK<br>(Port_G7)  | 43  | Input        | Clock output pin for SD card                   |

#### 3.22 CMOS Camera Interface

The CMSI has the following features:

- SXGA(1280×1024), 4VGA(1280×960), VGA(640×480), QVGA(320×240),

Special(320×180), QQVGA(160×120), CIF(352×288), QCIF(176×144)

- Input data format CRGB

- Input data sampling ratio 8-bit YUV4:2:2 or RGB888 if no color space conversion)

- Downscaling function

- 4VGA → VGA, QVGA, QQVGA

- VGA → QVGA, QQVGA

- QVGA → QQVGA

- Trimming function: Data can be trimmed to a desired size.

| Signal        | PIN | Input/Output | Function Remarks                                 |

|---------------|-----|--------------|--------------------------------------------------|

| L_D12(CMSPCK) | 111 | Input        | Clock input for CMOS sensor                      |

| L_D13(CMSHSY) | 109 | Input        | Horizontal synchronization input for CMOS sensor |

| L_D14(CMSHBK) | 107 | Input        | Valid data detect input for CMOS sensor          |

| L_D15(CMSVY)  | 105 | Input        | Vertical synchronization input for CMOS sensor   |

| L_D16(CMSD0)  | 101 | Input        | CMOS data driver line                            |

| L_D17(CMSD1)  | 99  | Input        | CMOS data driver line                            |

| L_D18(CMSD2)  | 97  | Input        | CMOS data driver line                            |

| L_D19(CMSD3)  | 95  | Input        | CMOS data driver line                            |

| L_D20(CMSD4)  | 91  | Input        | CMOS data driver line                            |

| L_D21(CMSD5)  | 89  | Input        | CMOS data driver line                            |

| L_D22(CMSD6)  | 87  | Input        | CMOS data driver line                            |

| L_D23(CMSD7)  | 85  | Input        | CMOS data driver line                            |

Attention: CMOS camera Interface uses some of the same pins as the LCDC data bus – so only 12bit colour (4096 display colours) is possible.

# 3.23 Melody/Alarm Generator

### Melody Generator

Based on the low-speed clock (32.768 kHz), clock wave forms can be generated at any frequency from 4 Hz to 5461 Hz and outputted from the MLDALM pin. By connecting a buzzer etc outside, melody sounds can easily be played.

### Alarm Generator

Can generate eight patterns of alarm output.

Can generate five types of fixed-interval interrupts (1 Hz, 2 Hz, 64 Hz, 512 Hz and 8192 Hz).

By connecting a buzzer etc outside, alarm sounds can easily be played.

| Signal              | PIN | Input/Output | Function Remarks        |

|---------------------|-----|--------------|-------------------------|

| MLDALM<br>(PORT C3) | 108 | Output       | Melody/alarm output pin |

# 3.24 Low Frequency Clock Output

| Signal             | PIN | Input/Output | Function Remarks               |

|--------------------|-----|--------------|--------------------------------|

| FSOUT<br>(PORT_C4) | 106 | Output       | Low frequency output clock pin |

# 4.0 Pin Allocation SODIMM 144 Connector

|             | IS10<br>J19154-144-XXA110X           |                                    |            |  |  |  |

|-------------|--------------------------------------|------------------------------------|------------|--|--|--|

| 1_          | GND01                                | GND02                              | 2          |  |  |  |

| 3_<br>5     | VDD3V3                               | VDD3V3                             | 6          |  |  |  |

| 7           | FUTURE_USE<br>PC7/I2C0DA/INT9/USBOCN | ETHLED1<br>ETHLED2                 | 8          |  |  |  |

| 9_          | PC6/I2C0CL/USBPON                    | ETHCT                              | 10         |  |  |  |

| 11<br>13    | GND03                                | GND04                              | 12         |  |  |  |

| 15          | SN6/USBHDP                           | ETHRXP                             | 16         |  |  |  |

| 17          | SN7/USBHDM<br>SR0/USBDDP             | ETHRXN<br>ETHTXP                   | 18         |  |  |  |

| 19_         | SR1/USBDDM                           | ETHTXN                             | 20         |  |  |  |

| 21<br>23    | GND05                                | GND06                              | 22         |  |  |  |

| 25          | PA3/KI3<br>PA2/KI2                   | PN7/U0RTSN/INTG<br>PN6/U0DTRN/INTF | 26         |  |  |  |

| 27          | PA1/KI1                              | PN5/UORIN/INTE                     | 28         |  |  |  |

| 29_         | PAO/KIO                              | PN4/U0DSRN/INTD                    | 30         |  |  |  |

| 31_<br>33   | GND07                                | GND08                              | 32         |  |  |  |

| 35          | PB3/KO3<br>PB2/KO2                   | PN3/U0DCDN<br>PN2/U0CTSN           | 36         |  |  |  |

| 37          | PB1/KO1/LCLAC                        | PN1/UORXD/SIROIN                   | 38         |  |  |  |

| 39_         | PB0/KO0                              | PNO/U0TXD/SIR0OUT                  | 40         |  |  |  |

| 41_<br>43   | GND09                                | GND10                              | 42         |  |  |  |

| 45          | PG7/SDC0CLK<br>PG6/SDC0CD            | PT5/U1RXD                          | 46         |  |  |  |

| 47          | PG6/SDC0CD<br>PG5/SDC0WP             | PT4/U1TXD<br>PT3/SP0DI             | 48         |  |  |  |

| 49_         | PG4/SDC0CMD                          | PT2/SP0D                           | 50         |  |  |  |

| 51_<br>53   | GND11                                | GND12                              | 52<br>54   |  |  |  |

| 55          | PG3/SDC0DAT3<br>PG2/SDC0DAT2         | PT1/SP0CLK<br>PT0/SP0FSS           | 56         |  |  |  |

| 57          |                                      | F7/I2C1DA/INTC/U2RXD               | 58         |  |  |  |

| 59_         | PG0/SDC0DAT0                         | PF6/I2C1CL/U2TXD                   | 60         |  |  |  |

| 61<br>63    | VDD3V3                               | VDD3V3                             | 62         |  |  |  |

| 65          | GND13<br>PD7/INTB/AN7/PY             | GND14<br>FUTURE USE                | 66         |  |  |  |

| 67          | PD6/INTA(TSI)/AN6/PX                 | FUTURE_USE                         | 68         |  |  |  |

| 69_<br>71   | PD5/AN5/MY                           | FUTURE_USE                         | 70<br>72   |  |  |  |

| 71<br>73    | PD4/AN4/MX                           | FUTURE_USE                         | 74         |  |  |  |

| 75          | GND15<br>SU4/LCLLP                   | GND16<br>PD3/AN3                   | 76         |  |  |  |

| 77_         | SU3/LCLFP                            | PD2/AN2                            | 78         |  |  |  |

| 79_<br>81   | SU1/LCLAC                            | PD1/AN1                            | 80         |  |  |  |

| 83          | SU0/LCLCP                            | PD0/AN0                            | 84         |  |  |  |

| 85          | GND17<br>LC_D23                      | GND18<br>PM3/I2S1MCLK              | 86         |  |  |  |

| 87_         | LC_D22                               | PM2/I2S1DAT0                       | 88         |  |  |  |

| 89_<br>91   | LC_D21                               | PM1/I2S1CLK                        | 90         |  |  |  |

| 93          | LC_D20                               | PM0/I2S1WS                         | 94         |  |  |  |

| 95          | GND19<br>LC D19                      | GND20<br>PL3/I2S0MCLK/SP1DI        | 96         |  |  |  |

| 97_         | LC_D18                               | PL2/I2S0DATI/SP1DO                 | 98         |  |  |  |

| 99_<br>01   | LC_D17                               | PL1/I2SOCLK/SP1CLK                 | 100        |  |  |  |

| .03         | LC_D16                               | PL0/I2S0WS/SP1FSS                  | 104        |  |  |  |

| 05          | GND21<br>LC_D15                      | GND22<br>PC4/FSOUT/PWM3OUT         | 106        |  |  |  |

| 07_         | LC_D14                               | PC3/MLDALM/PWM1OU                  | 108        |  |  |  |

| 09_<br>11   | LC_D13                               | PC2/PWE                            | 110<br>112 |  |  |  |

| 13          | LC_D12                               | RESET                              | 114        |  |  |  |

| 15          | GND23<br>LC_D11                      | GND24<br>SP5/TDO_JTAG              | 116        |  |  |  |

| 17_         | LC_D10                               | SP4/RTCK_JTAG                      | 118        |  |  |  |

| 19_         | LC_D9                                | SPO/TCK_JTAG                       | 120        |  |  |  |

| 23          | LC_D8<br>GND25                       | SP1/TMS_JTAG                       | 124        |  |  |  |

| 25          | GND25<br>LC_D7                       | GND26<br>SP2/TDI_JTAG              | 126        |  |  |  |

| 27_         | LC_D6                                | SP3/TRSTN_JTAG                     | 128        |  |  |  |

| .29<br>.31  | LC_D5                                | SN2/SELJTAG                        | 130<br>132 |  |  |  |

| 33          | LC_D4                                | SM7/AM1_JTAG                       | 134        |  |  |  |

| 35          | GND27<br>LC_D3                       | GND28<br>VIN3V3                    | 136        |  |  |  |

| 37_         | LC_D2                                | VIN3V3                             | 138        |  |  |  |

| .39_<br>.41 | LC_D1                                | VIN3V3                             | 140<br>142 |  |  |  |

| 41_         | LC_D0                                | VIN3V3                             | 144        |  |  |  |

| -           | GND29                                | GND30                              |            |  |  |  |

### **PINOUT (1/5)**

| Numper of | Pin Name | Input/Output | Function Remarks                                                                                 |

|-----------|----------|--------------|--------------------------------------------------------------------------------------------------|

| Pin       | ONE      |              |                                                                                                  |

| 1-2       | GND      |              | Ground                                                                                           |

| 3-4       | VDD3V3   | Output       | Power                                                                                            |

| 5         | nc       | Output       | leave open                                                                                       |

| 6         | LED1     | Output       | Ethernet LED1: Speed LED                                                                         |

| 7         | USB_OC   | Input/Output | PC7: I/O port                                                                                    |

|           |          | Input/Output | I2C0DA: I2C data I/O                                                                             |

|           |          | Input        | INT9: Interrupt request pin9: an interrupt request pin that                                      |

|           |          |              | can program the rising/falling edge                                                              |

|           |          | Input        | USBOCn: Over Current detect for USB Host                                                         |

| 8         | LED2     | Output       | Ethernet LED2: Link/Active LED                                                                   |

| 9         | USB_PON  | Input/Output | PC6: Port C6: I/O port                                                                           |

|           |          | Input/Output | I2C0CL: I2C clock I/O                                                                            |

|           |          | Output       | USBPON: Power On Enable for USB Host                                                             |

| 10        | CT       |              | Ether                                                                                            |

| 11-12     | GND      | -            | Ground                                                                                           |

| 13        | USB HDP  |              | USB Host pin (D+)                                                                                |

| 14        | RXP      |              | Ethernet                                                                                         |

| 15        | USB HDM  |              | USB Host pin (D-)                                                                                |

| 16        | RXN      |              | Ethernet                                                                                         |

| 17        | USB_DDP  |              | USB Device pin (D+)                                                                              |

| 18        | TXP      |              | Ethernet                                                                                         |

| 19        | USB DDM  |              | USB Device pin (D-)                                                                              |

| 20        | TXN      |              | Ethernet                                                                                         |

| 21-22     | GND      |              | Ground                                                                                           |

|           | Port A3  |              | PA3: Input port                                                                                  |

| 23        | POR A3   | Input        |                                                                                                  |

|           |          |              | Key input KI3: Pin for key-on wake up (with Schmitt input and pull-up resistor)                  |

| 24        | Port N7  | Input/Output | PN7: I/O port                                                                                    |

| 24        | POIL IN/ |              | U0RTSn: Output modem control line RTD(Request To                                                 |

|           |          | Output       |                                                                                                  |

|           |          | Innut        | Send) INTG: Interrupt request pin G: an interrupt request pin that                               |

|           |          | Input        | can program the rising/falling edge                                                              |

| 25        | Port A2  | Innut        | Port A2: Input port                                                                              |

| 25        | POILAZ   | Input        | Key input KI2: Pin for key-on wake up                                                            |

|           |          |              | (with Schmitt input and pull-up resistor)                                                        |

| 26        | Dort NG  | Innut/Output | PN6: I/O port                                                                                    |

| 26        | Port N6  | Input/Output | U0DTRn: Output modem control line DTR (Data Terminal                                             |

|           |          | Output       | Ready)                                                                                           |

|           |          | Innut        |                                                                                                  |

|           |          | Input        | INTF: Interrupt request pin F: an interrupt request pin that can program the rising/falling edge |

| 27        | Dort A1  | Innut        | Port A1: Input port                                                                              |

| 21        | Port A1  | Input        | Key input KI1: Pin for key-on wake up                                                            |

|           |          |              | (with Schmitt input and pull-up resistor)                                                        |

| 28        | Dort NE  | Input/Output | PN5: I/O port                                                                                    |

| 20        | Port N5  |              |                                                                                                  |

|           |          | Input        | U0RIn: Modem status signal RI (Ring Indicator)                                                   |

|           |          | Input        | INTE: Interrupt request pin E: an interrupt request pin that                                     |

| 20        | Dort AO  | Input        | can program the rising/falling edge Port A0: Input port                                          |

| 29        | Port A0  | Input        |                                                                                                  |

|           |          |              | Key input KI0: Pin for key-on wake up                                                            |

|           | 5 (1)(4  | 1 1/0 1 1    | (with Schmitt input and pull-up resistor)                                                        |

| 30        | Port N4  | Input/Output | PN4: I/O port                                                                                    |

|           |          | Input        | U0DSRIn: Modern status signal DSR (Data Set Ready)                                               |

| 1         |          | Input        | INTD: Interrupt request pin D: an interrupt request pin that                                     |

| 04.00     | OND      |              | can program the rising/falling edge                                                              |

| 31-32     | GND      | -            | Ground                                                                                           |

### PINOUT (2/5)

| Numper of | Pin Name | Input/Output                 | Function Remarks                                                                        |

|-----------|----------|------------------------------|-----------------------------------------------------------------------------------------|

| Pin       |          |                              |                                                                                         |

| 33        | Port B3  | Output<br>Output             | PB3: Output port KO3: Key out pins (open-drain can be set)                              |

| 34        | Port N3  | Input/Output<br>Input        | PN3: I/O port<br>U0DCDn: Modem status signal DCD (Data Carrier Detect)                  |

| 35        | Port B2  | Output                       | PB2: Output port                                                                        |

|           | 2 (112   | Output                       | KO2: Key out pins (open-drain can be set)                                               |

| 36        | Port N2  | Input/Output<br>Input        | Port N2: I/O port<br>U0CTSn: UART function 0 data can be transmitted<br>(Clear to send) |

| 37        | Port B1  | Output                       | PB1: Output port                                                                        |